Seat Number .....

| NameStu | Ident ID |

|---------|----------|

|---------|----------|

## Midterm Examination Semester 1 Year 2018

Course: CPE 223 Digital Electronics and Logic Design

Group 31, 32

Date: 5 October 2018 13.00-16.00

### Instruction

1. Calculator, books, documents, and notes are not allowed in the examination room.

2. Carefully read the explanation in each problem and then answer each question.

3. Do not take the examination sheets out of the examination room.

4. This examination has 11 pages including this page (6 problems, 40 points).

- Student must raise your hand to ask for permission before leaving the room.

- Student must not take the exam and booklet outside the room.

- The highest punishment can be applied if the cheating is discovered.

Port In

(Asst. Prof. Suthathip Maneewongvatana, Ph.D.)

This exam is approved by the Computer Engineering Department's committees

(Assoc. Prof. Dr. Natasha Dejdumrong)

Program chair

Date.....Year....

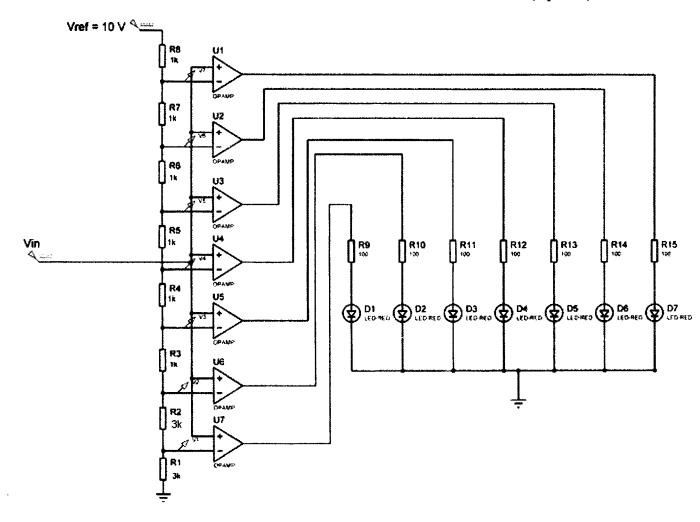

## 1. Consider the circuit below:

•

•

(6 points)

Figure 1

# a) Identify the voltage level measured at position v1-v7

(4 points)

| Position | Voltage Level (Volt) |

|----------|----------------------|

| vl       |                      |

| v2       |                      |

| v3       |                      |

| v4       |                      |

| v5       |                      |

| v6       |                      |

| v7       |                      |

b) Which LED(s) will bright if the voltage level for Vin = 5.2 V, and 8 V, respectively (2 points)

2. For the following Boolean function:

•

\*

(6 points)

a.  $F(W, X, Y, Z) = \sum m(2, 4, 5, 6, 10) + D(12, 13, 14, 15)$  Simplify the Boolean function F into Sum of Products form. (2 points)

b.  $F(A, B, C, D) = \sum m(2, 3, 5, 6, 7, 10, 11, 13, 14)$  Simplify the Boolean function F into Product of Sums form (4 points)

,a

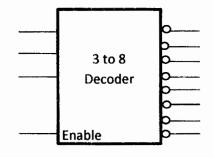

c. F(A, B, C, D) = AB + BCD implement the Boolean expression by using 3 to 8 decoders (see the datasheet of IC 74138 in the last page) and NAND gate (4 points)

•

.

3. Given the Boolean expression  $F(W, X, Y, Z) = WX\overline{Y} + \overline{WXY} + (W \oplus Y)$  (8 points)

| W | X | Y | WXŸ | WXY | W⊕Y | f |

|---|---|---|-----|-----|-----|---|

| 0 | 0 | 0 |     |     |     |   |

| 0 | 0 | 1 |     |     |     |   |

| 0 | 1 | 0 |     |     |     |   |

| 0 | 1 | 1 |     |     |     |   |

| 1 | 0 | 0 |     |     |     |   |

| 1 | 0 | 1 |     |     |     |   |

| 1 | 1 | 0 |     |     |     |   |

| 1 | 1 | 1 |     |     |     |   |

a) Complete the truth table for this expression

.

b) Simplify the Boolean expression and implement the all NAND circuit for this expression. (1 points)

C) Implement the Boolean expression by using 2 to 1 multiplexer using "W" as the selector and other necessary logic gates (4 points)

(3 points)

4. Show the steps of addition or subtraction (use 2's complement representation) between two 4 bit binary numbers A and B. Indicate whether an overflow occurs. (3 points)

a) A+B given A=0111, B=0101

•

.

b) A-B given A=0011, B=1001

(1 point)

c) A+B given A=0011, B=1110

7

(1 point)

(1 point)

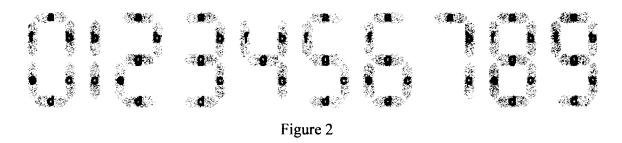

5. Figure 2. represents 7-segment (*a-g*) displaying number 0-9 (0000-1001)

a) Write the truth table representing 4bit binary input and the outputs for only two segments (segment B and C) using a common Cathode 7-segment (use logic 1 to turn on the leds) (4 points)

| Number | 4 bit binary     | b | С |

|--------|------------------|---|---|

|        | $(B_3B_2B_1B_0)$ |   |   |

| 0      | 0000             |   |   |

| 1      | 0001             |   |   |

| 2      | 0010             |   |   |

| 3      | 0011             |   |   |

| 4      | 0100             |   |   |

| 5      | 0101             |   |   |

| 6      | 0110             |   |   |

| 7      | 0111             |   |   |

| 8      | 1000             |   |   |

| 9      | 1001             |   |   |

b) Minimize the Boolean function in <u>Sum of Product form (SOP</u>) form to generate the output for segment b and c.

,

,

(2 points)

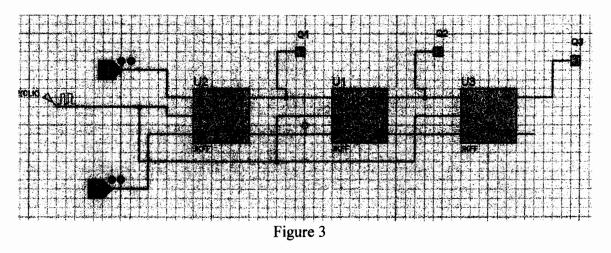

6. Consider the circuit in Figure 3.

(5 points)

a) Draw the timing diagram representing clock, Q1, Q2, and Q3. Assume time delay for each JK FF is equal to ¼ of clock cycle and the initial state for Q1, Q2, Q3 are '0'. (4 points)

b) What is the sequence that this circuit counts  $(Q_1Q_2Q_3)$ ? (1 points)

#### FUNCTIONAL DESCRIPTION

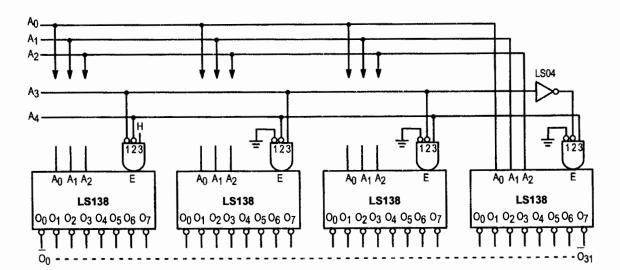

The LS138 is a high speed 1-of-8 Decoder/Demultiplexer fabricated with the low power Schottky barrier diode process. The decoder accepts three binary weighted inputs (A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>) and when enabled provides eight mutually exclusive active LOW Outputs (O<sub>0</sub>-O<sub>7</sub>). The LS138 features three Enable inputs, two active LOW (E<sub>1</sub>, E<sub>2</sub>) and one active HIGH (E<sub>3</sub>). All outputs will be HIGH unless E<sub>1</sub> and E<sub>2</sub> are LOW and E<sub>3</sub> is HIGH. This multiple enable function allows easy parallel ex-

pansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four LS138s and one inverter. (See Figure a.)

The LS138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active HIGH or active LOW state.

| INPUTS |                |    |                |                | OUTPUTS        |                |    |    |    |    |    |    |    |

|--------|----------------|----|----------------|----------------|----------------|----------------|----|----|----|----|----|----|----|

| Ē1     | E <sub>2</sub> | E3 | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | O <sub>0</sub> | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| Н      | Х              | Х  | X              | X              | X              | н              | н  | н  | н  | н  | н  | н  | н  |

| х      | н              | х  | х              | х              | х              | н              | н  | н  | н  | н  | н  | н  | н  |

| х      | Х              | L  | X              | х              | х              | н              | н  | н  | н  | н  | н  | н  | н  |

| L      | L              | н  | L              | L              | L              | L              | н  | н  | н  | н  | н  | н  | н  |

| L      | L              | н  | н              | L              | L              | н              | L  | н  | н  | н  | н  | н  | н  |

| L      | L              | н  | L              | н              | L              | н              | н  | L  | н  | н  | н  | н  | н  |

| L      | L              | н  | н              | н              | L              | н              | н  | н  | L  | н  | н  | н  | н  |

| L      | L              | н  | L              | L              | н              | н              | н  | н  | н  | L  | н  | н  | н  |

| L      | L              | н  | н              | L              | н              | н              | н  | н  | н  | н  | L  | н  | н  |

| L      | L              | н  | L              | н              | н              | н              | н  | н  | н  | н  | н  | L  | н  |

| L      | L              | н  | İн             | н              | н              | н              | н  | н  | н  | н  | н  | н  | L  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care